复杂计算的CPU和并行计算的GPU,究竟谁是未来?

在计算世界的赛道上,NVIDIA 靠着 GPU 海量并行能力几乎席卷了 AI 训练、推理、图形渲染等所有高吞吐场景,而 Intel 和 AMD 则把重心放在CPU单核性能、分支预测、乱序执行和大缓存的极致打磨上。很多人会问:这两条路到底谁更接近未来?答案其实没有那么非黑即白,因为它们本质上解决的是完全不同的问题。

并行计算为什么这么猛?

过去十年深度学习把计算需求彻底重塑,矩阵乘法、注意力机制、Transformer 这些核心操作天生就能拆成无数小块同时计算,GPU 正好为此而生。几千上万的核心一起干活,再配上 HBM 高带宽内存,形成了碾压级的吞吐能力——相比于延迟问题,并行计算更重视带宽。大模型动辄几万张卡的训练规模,让很多人觉得未来就是并行计算的天下。

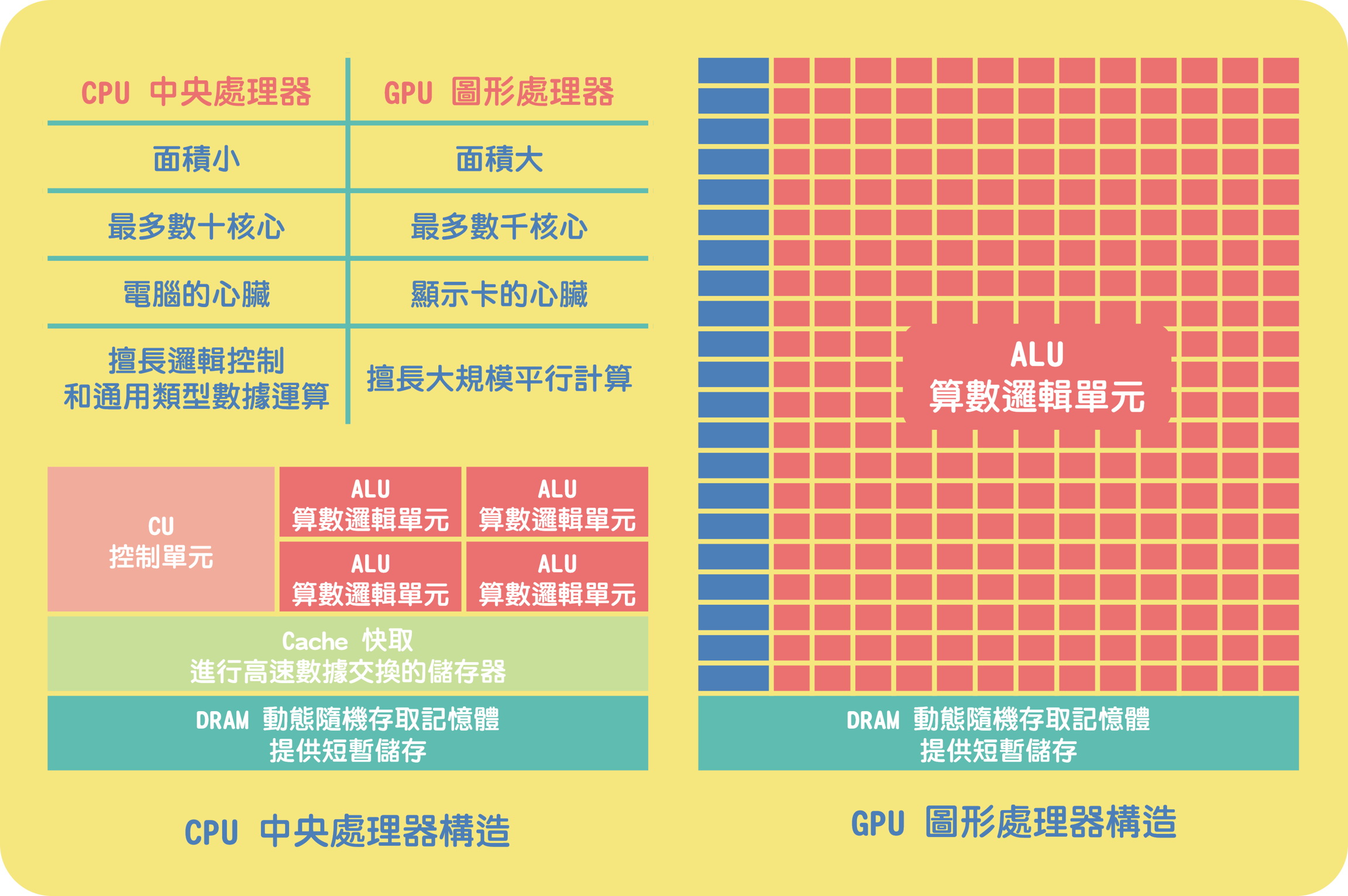

CPU与GPU的本质差异

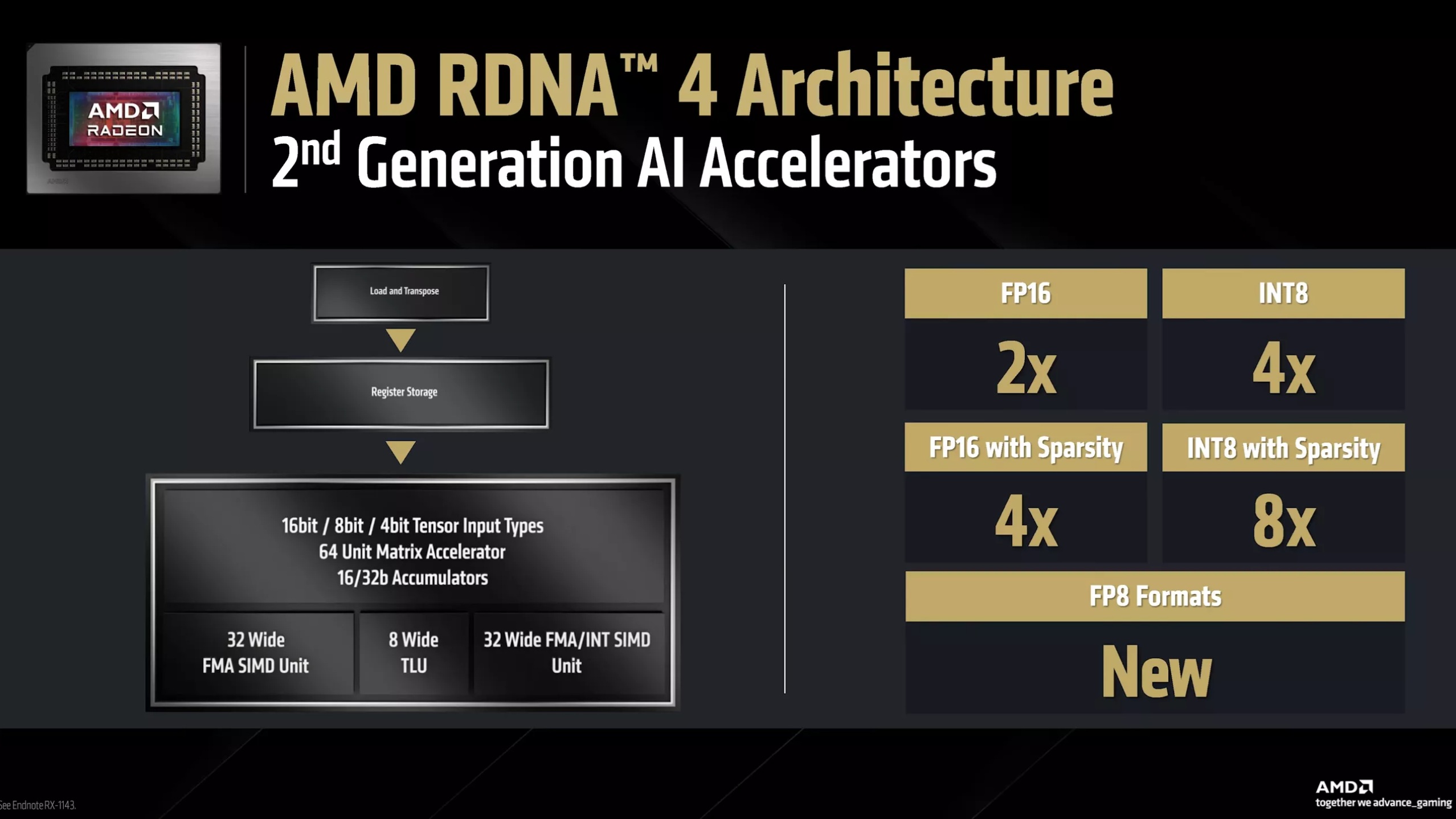

GPU 的并行算力强大,还体现在对不同精度的灵活支持上。传统 FP32(单精度)适合通用计算,但 AI 训练和推理越来越依赖低精度格式来换取速度和能效。现代 GPU 通过专用矩阵加速单元(如 NVIDIA 的 Tensor Cores 或 AMD 的 AI 加速器 / Matrix Cores / WMMA 单元)来高效处理这些操作,能支持 FP16、BF16(脑浮点)、INT8,甚至 FP8 等更低精度格式。低精度让计算密度大幅提升——在同样的硅片面积(晶体管数量/芯片面积)下,低精度格式(如 FP8)允许 GPU 执行远更多的浮点运算,同时大幅降低内存占用和带宽压力。这直接推动了大模型的规模爆炸:训练速度更快、推理更省电、部署成本更低。简单说,并行计算的“猛”不只靠核心数量,还靠精度降维打击,让海量数据以更高效的方式被“嚼碎”处理。

复杂计算始终位于舞台中央!

但是,这不代表世界全部都是并行计算的,现实里还有大量场景根本跑不出高并行度。数据库的事务处理、游戏里单线程的 AI 决策和物理模拟、传统高性能计算里的稀疏矩阵和图计算、浏览器渲染、编译器、Java/Go 后端服务等等,这些地方真正吃的是“每一条指令要多快到达、多快执行完”,而不是“同时干多少条”。它们更依赖单核 IPC、极低的缓存延迟、聪明的分支预测和足够大的乱序窗口。这正是 AMD Zen 系列(尤其是3D V-Cache系列)和 Intel 最新架构拼命优化的方向。

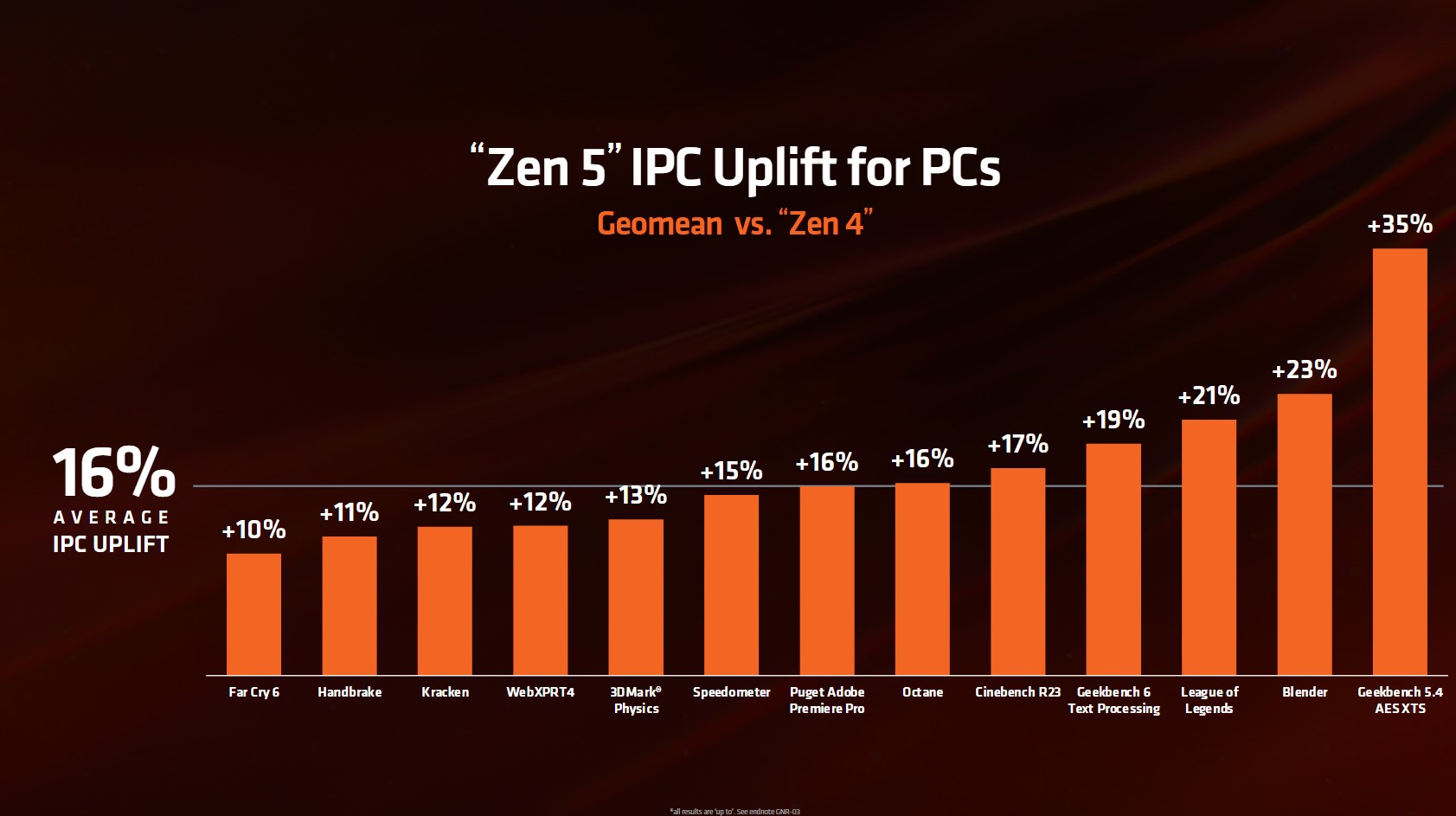

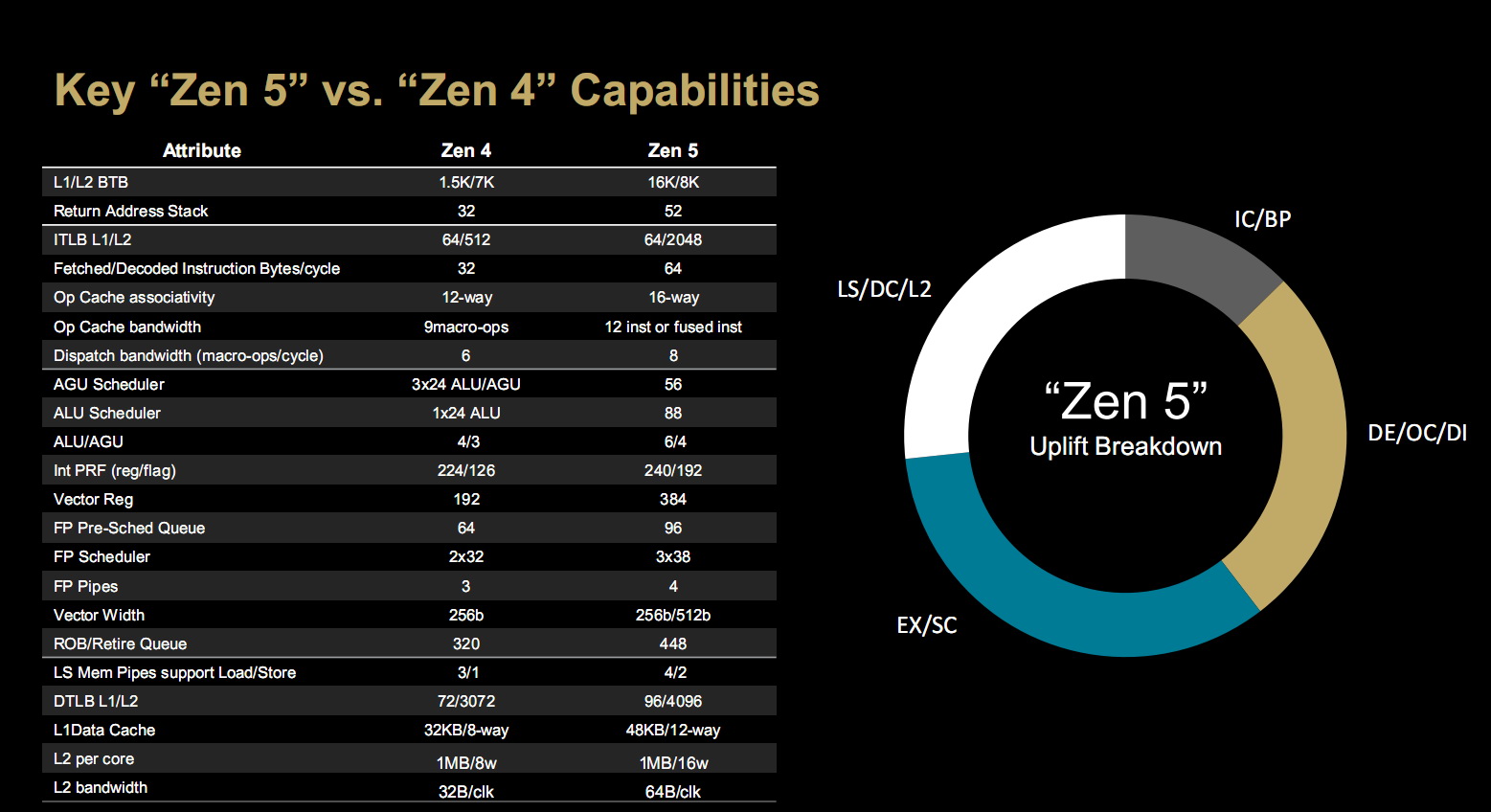

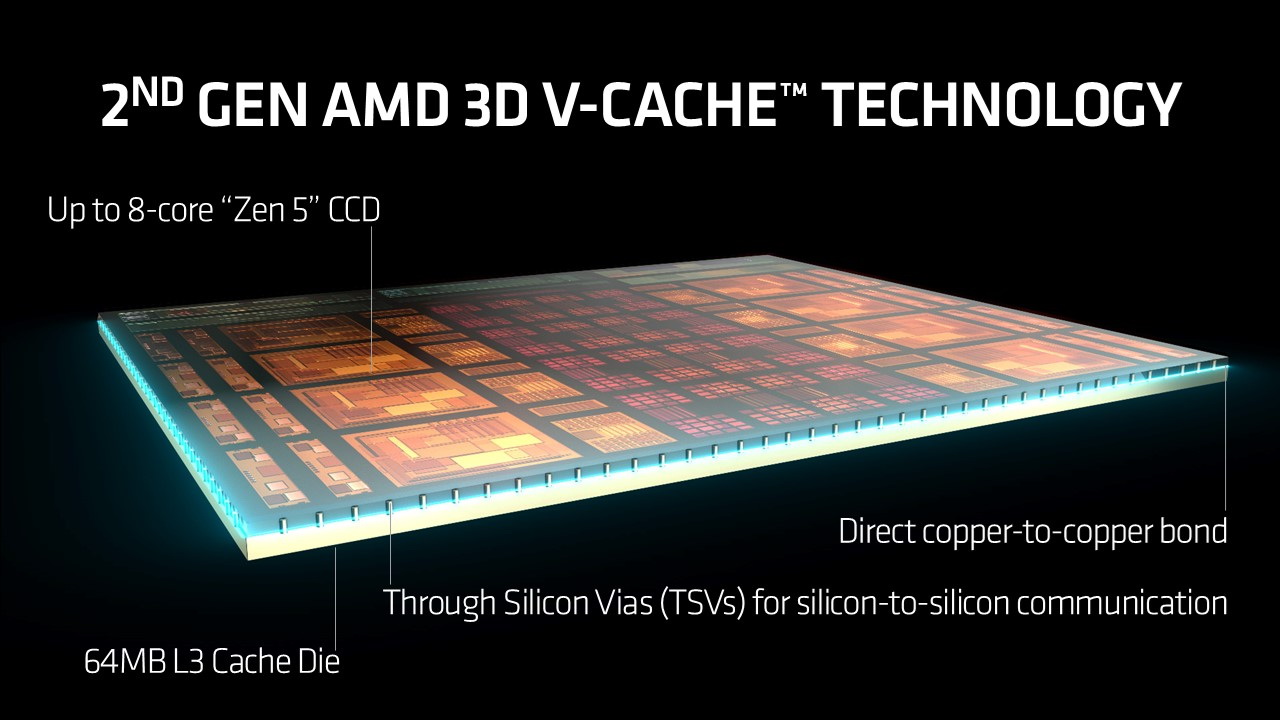

比如AMD当下的Zen 5架构(锐龙9000系列及线程撕裂者 9000系列)带来了显著升级,核心数量最大可达 96 个,并引入两步前瞻分支预测、ALU从4 个增到 6 个提升整数吞吐 50%、向量引擎浮点管道从 3 增到 4、AVX-512 增强支持、更大的 L3 缓存,IPC 平均提升 16%,同时支持更高的内存速率。这些优化让 Zen 5 在单线程延迟敏感任务和游戏中继续强势,尤其3D V-Cache的大缓存是游戏玩家最好的选择。

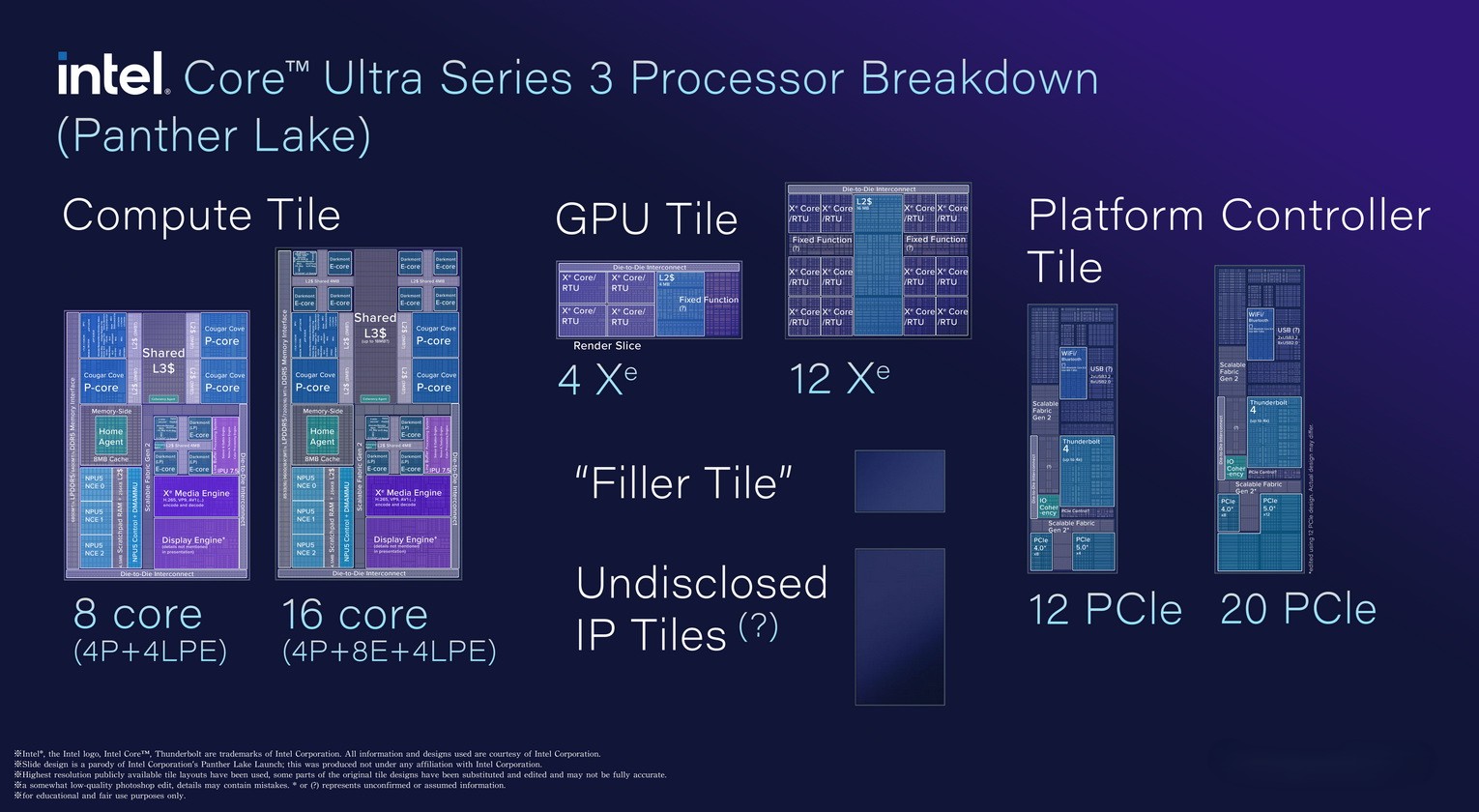

Intel 最新一代则以 Arrow Lake(酷睿Ultra 200 系列)和Panther Lake(酷睿Ultra 300)为主。Arrow Lake 采用 Chiplet 设计、Lion Cove P 核 + Skymont E 核混合、TSMC N3B 工艺 compute tile、独占 DDR5 支持、集成 Xe2/Xe3 图形;Panther Lake 进一步统一 Lunar Lake 的超低功耗效率与 Arrow Lake 的性能,基于 Intel 18A 工艺、可扩展 8/16 核配置、Xe3 图形最高 12 核(接近 RTX 4050 独显)、NPU 优化保持高能效、多线程性能提升 60%、游戏提升 77%。并且,这两代CPU都非常强调混合核心效率、AI 加速和图形集成,在低延迟、企业服务和移动场景中保持着强大的竞争力。

如果非要对比,那就是并行计算追求最大吞吐,复杂计算追求最低延迟——两条路很难完全互相取代,就像高速公路上的货车和跑车,谁也替代不了谁。

缓存战争:瓶颈永远都在

另外,真正决定算力天花板的,其实一直是数据能不能及时送到计算单元面前——缓存与内存的永恒拉锯战。

在芯片内部,L1 缓存最快但容量极小,只有几十 KB,基本只够缓存正在运行的指令和数据;L2 缓存容量大一些,每个核心独享,延迟控制在十几个周期;L3 缓存则是所有核心共享的“大水池”,AMD 把 3D V-Cache 做到上百 MB,让游戏和很多缓存敏感负载直接起飞。

在芯片外部,为高带宽而生的HBM,最新的HBM4 预期单栈 2.2 TB/s 左右带宽,听起来很夸张,但放在几千上万核心同时“饿肚子”的场景下,仍然远远不够。至于普通的 DDR5 带宽就更有限,只有几百 GB/s,延迟还高得多。

不管工艺怎么缩小,冯·诺依曼瓶颈(计算和存储分离)始终横在那里。计算单元越并行,对“数据即时送达”的渴求就越极端。所以你可以看到GPU 拼命堆 HBM 层数和 NVLink 互联,CPU 则疯狂堆 L3 容量,甚至愿意牺牲一点频率也要换来更大的本地数据池。这场缓存战争还会持续很多年,因为“让正确的数据在正确的时间出现在正确的地方”永远是计算的终极难题,目前谁都没能彻底解决。

未来不是你死我活,而是两条腿走路

未来的图景大概率不是一方彻底取代另一方,而是高度分工又紧密协同。吞吐怪兽的任务交给 GPU 和专用加速器,延迟敏感、分支密集、难以并行的活儿还是交给复杂 CPU。大部分真实世界应用都会是 CPU + GPU + NPU 的异构组合,长期共存——两条腿走路,才是计算真正的未来。